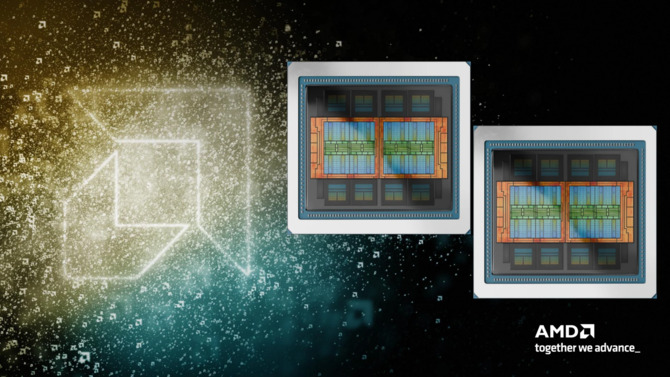

AMD CDNA 4 — Описание архитектуры для ускорителей для искусственного интеллекта на примере систем из серии Instinct MI350

AMD на пресс -конференции представила системы из серии Instinct MI350 на основе архитектуры CDNA 4, которая была разработана для максимального использования искусственного интеллекта и повышения энергоэффективности. Мы узнали подробности изменений в построении этих ускорителей и их прямое влияние на производительность. Поэтому я приглашаю вас к обширному описанию архитектуры кДНК 4 и ее широких возможностей.

AMD представила акселераторы из серии Instinct MI350, а вместе с ними архитектура кДНК 4, на которой мы сосредоточимся здесь. Мы узнали подробности об изменениях в построении этих систем и их влиянии на производительность.

AMD RADEON RX 9060 XT против NVIDIA GEFORCE RTX 5060 TI GRAPHICS

Чтобы понять работу систем из серии Instinct MI350 и архитектуры CDNA 4, стоит проанализировать, как они построены в технологии Cowos, то есть многослойной упаковке. Верхний слой состоит из двух чипов расчета, в которых есть два блока и/o вместе с межконтактом AMD Infinity Fabric, соединяющими эти блоки и предлагая емкость 5,5 ТБ/с. Восемь костей памяти HBM3E с общей емкостью 8 ТБ/SI расположены 288 ГБ расположены вокруг них. Каждый расчет чип делится на четыре блока XCD (комплекс -ускоритель -комплекс), каждый из которых содержит 32 единицы Cu (вычисления), а каждый блок Cu состоит из 4 матричных ядер. Встроенная память кэша L2 имеет емкость 4 МБ на блок XCD. В общей сложности вся система акселераторов ИИ включает в себя 8 блоков XCD, которые дают 256 единиц Cu и 1024 ядра матрицы (эквивалентно ядрам Nvidia Tensor).

Amd Ryzen Z2 A и Ryzen Ai Z2 Extreme — Компания подтверждает спецификацию процессоров для консолей Rog Xbox Ally

Каждый блок XCD имеет прямой доступ к соединению Infinity Fabric, который предоставляет 16 линий PCIe 5.0 и семь соединений x16 Infinity Fabric Link 4. Generation с полосой пропускной способности 1075 ГБ/с каждая. Память HBM3E также подключена к взаимосвязи через кэш бесконечности с общей емкостью 256 МБ. Чисы были сделаны в технологическом процессе TSMC N3P, в то время как блоки ввода/вывода были созданы в литографии TSMC N6. Эта конструкция позволяет разделить программу системы, позволяя вам использовать различные режимы вычислений (CPX, DPX, QPX, SPX) в комбинации с конфигурациями памяти NUMA (NPS1 и NPS2). Режим CPX рассматривает GPU как один, DPX делит его на две части, QPX на четыре, а SPX представляет самые маленькие логические фрагменты, то есть отдельные блоки XCD. Режимы NPS определяют, как разделить память HBM3E: NPS1 является одним из распространенных доменов NUMA и NPS2 — два.

PlayStation Handheld с новыми деталями спецификации. Спецификация консоли состоит в том, чтобы иметь сходство с AMD Strix Halo

Например, CPX+NPS2 использует полный потенциал GPU с делением памяти на две части, DPX+NPS2 предлагает два независимых экземпляра с выделенной памятью (деление между двумя чипсами), а QPX+NPS2 позволяет четыре экземпляра, делящих два домена памяти. SPX+NPS1 означает использование отдельных блоков XCD для обработки отдельных задач, но с одним доменом NUMA. На практике это позволяет вам запустить полную модель LLM с 520 миллиардами параметров по всей системе или восьми моделей LLAM 3.1, 70 миллиардов параметров независимо, каждый из которых на отдельном блоке XCD.

AMD FSR Redstone — Компания раскрывает технологический пакет на основе машинного обучения. Доступность только для карт RDNA 4

AMD подчеркивает, что архитектура CDNA 4 также вводит расширенные возможности в размере страниц памяти UTC1 и UTC2, которые отвечают за организацию и разделение внутренней памяти системы. Кроме того, использовались оптимизации в декодировании данных и были расширены потоки памяти, что позволяет вам поддерживать полную емкость при более низком уровне и напряжении, что снижает потребление энергии — благодаря которой система инстинкта MI350x потребляет на 30% меньше энергии при чтении данных из памяти HBM3E. Что касается вычислительных единиц (Cu), наиболее важными изменениями являются парные разряды числа матричных операций в смешанной точке, выполненных на тактовой такте, что значительно ускоряет умножение матрицы (GEMM) и двойное увеличение способности к трансцендентальной функции, что приводит к улучшению эффективности механизмов обращения.

Amd Ryzen Threadripper (Pro) 9000 — Официальная презентация процессоров и систем Hedt Zen 5 для рабочих станций

Служба низкого порка численных форматов FP4 и FP6 в соответствии со спецификацией OCP MX, обеспечивая точное масштабирование расчетов на уровне аппаратного обеспечения, и новые инструкции DOT2 DOT2, которые выполняют также введены операции по эффективности FP32, и накапливались для FP32, обеспечивающие компромисс между эффективностью и точными. Локальная память LDS была увеличена до 160 кб и получила большую мощность, что снижает нагрузку на память HBM3E, и была улучшена прямая загрузка данных от глобальной памяти в LDS. В результате гибельная емкость показания данных из памяти HBM3E была увеличена на единицу Cu на 50% по сравнению с предыдущим поколением. В области квантования появились новые механизмы: аппаратное стохастическое округление при преобразовании FP16/BF16 в FP32, который ограничивает ошибки квантования, руководство LOP3, которое позволяет пользователю определять неэндирдирующие логические операции и новые инструкции MIN/MAX, позволяющие более гибкому обработке значения NAN (Not Not Extrails Supports Supports Supports Supplysing и контролируют поля и контролирующие поля и контролирующие поля и контролирующие поля и контролирующие поля.

2 нм процесс TSMC с технологией GAA. AMD фокусируется на эффективности и энергоэффективности на серверах будущего

Наибольшее увеличение емкости архитектуры кДНК 4 на примере системы инстинкта MI355X применяется к матричным операциям в форматах FP16/BF16, FP8 и Int8/Int4, где было сообщено о почти двойном улучшении (x1,9) против Instinct Mi300x. Подводя итог крупнейшей новизны является поддержкой форматов FP6 и FP4, чье более раннее поколение вообще не поддерживало и улучшение в разделении графических процессоров на одиночные, независимые экземпляры. В то же время, в классических форматах плавающей запятой (FP32, FP64) не было зарегистрировано никакого прогресса, что предполагает, что новые графические процессоры четко оптимизированы для расчетов ИИ и обработки с низким уровнем питания, а не традиционного рынка HPC. Кроме того, заметно ослабить эффективность FP64 в матричных операциях — только 128 флопов/Cu в Instinct MI355X — что указывает на сознательную отставку в результате развития двойной точности для энергоэффективности и сосредоточенности на задачах, связанных с искусственным интеллектом.

Источник: AMD, PurePC