AMD EPYC VENICE — Новая информация о спецификациях и энергопотреблении процессоров сервера Zen 6 и Zen 6C

Последним поколением процессоров AMD EPYC Server, которые дебютировали в 2024 и 2025 годах, являются Epyc Turin (zen 5), Epyc Turin-X (zen 5 + 3d V-ke) и Epyc Turin-Dense (zen 5c). Однако производитель, безусловно, уже находится на продвинутой стадии работы над следующим поколением, которая займет кодовое название Epyc Venice. На этот раз будет использоваться микроархитектура Zen 6 и Zen 6C. В сети появились новые детали об их структуре и спецификации.

Новая информация появилась в сети о процессах AMD Epyc Epyc Venice, которые будут использовать микроархитектуру Zen 6 и Zen 6C. В зависимости от типа ядер мы будем получать подразделения с максимум 96 дзен 6 или 256 ядер дзен 6C.

Предстоящие процессоры EPYC AMD выиграют от 2 нм процесса TSMC. AMD укрепляет свое сотрудничество с этой компанией

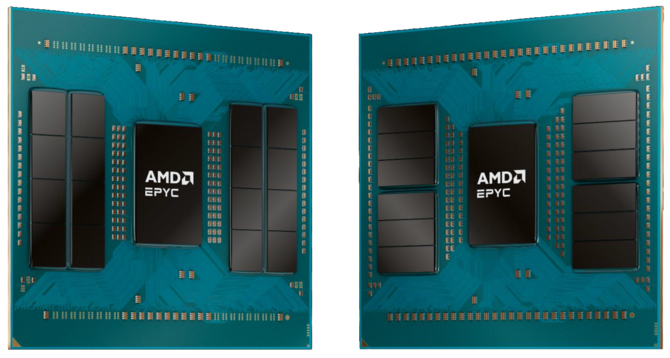

Мы узнали новые подробности о строительстве и спецификациях процессоров AMD EPYC Venice Server, которые выиграют от микроархитектуры Zen 6 и Zen 6C. Фотографии с китайского веб -сайта Baidu представляют некоторые данные о Epyc Venice Systems. Варианты с ядрами Zen 6 должны предлагать до 8 блоков CCD и до 96 ядер (и 192 потоков), в то время как единицы, работающие на ядрах Zen 6C, также получат до 8 кластеров CCD, но в конфигурации с максимумом 256 ядер и 512 потоков. Таким образом, процессоры Epyc Venice Zen 6 будут иметь 8 CCD, где каждый CCD будет оснащен 12 ядрами, в то время как CCD с ядрами Zen 6C будет иметь ровно 32 на борту. Если эта информация подтверждена, то EPYC Venice с ядрами Zen 6 будет иметь меньше кластеров CCD по сравнению с Epyc Turin — 8 Contra. Это увеличится для каждого кластера ПЗС. Это может, но не должно указывать, что аналогичное решение также будет использоваться в потребительском рисе (потому что это сказано об увеличении количества ядер в кластере ПЗС с 8 до 12).

AMD EPYC TURIN — было представлено новое поколение серверных процессоров, в котором используются ядра Zen 5 и Zen 5C

Генерация венеции Epyc с ядрами Zen 6 не имела бы (по крайней мере, в начале) конфигурации с 128 ядрами, как это было с Epyc Turin (EPYC 9755). С другой стороны, AMD планирует другие изменения в строительстве этих процессоров. На приведенной выше фото представлен фрагмент процессора Epyc Venice с ядрами Zen 6 (вы можете увидеть 12 ядер на кластере CCD). По крайней мере два блока и/O, где он был одним чипом, было размещено между ПЗС. Таким образом, Epyc Venice будет иметь больше вариантов с точки зрения ввода/вывода по сравнению с более ранними поколениями. Следующим изменением является то, что кэш L3 емкость памяти. Согласно графике, доступной в сети, каждый блок CCD теперь должен предлагать 128 МБ кэш L3, который с использованием 8 CCD-кластеров будет привести к примерно 1 ГБ памяти L3, и это без использования 3D-технологии 3D-упаковки 3D V-CIEM. Для сравнения, Top Epyc Turin — EPYC 9755 — имел 512 МБ кэш L3. Последняя часть информации применяется к розеткам и TDP. Похоже, что венеция AMD Epyc с ядрами Zen 6 будет соответствовать основанию SP8, а TDP единиц состоит в том, чтобы колебаться между 350 и 400 Вт. В свою очередь, венеция Epyc с ядрами Zen 6C будет совместима с Socket SP7, а их TDP будет достигнут около 600 Вт. Если информация будет подтверждена, мы обнаружим, что валена на достигнут.

SP8: до 128 ядер Zen 6C с 128 МБ на ПЗС (96 CRE для моделей Zen 6), 350-400 Вт

SP7: до 256 ядер Zen 6C, ~ 600 Вт

— bionic_squash (@squashbionic) 10 мая 2025 года

Источник: Wccftech, x @squashbionic