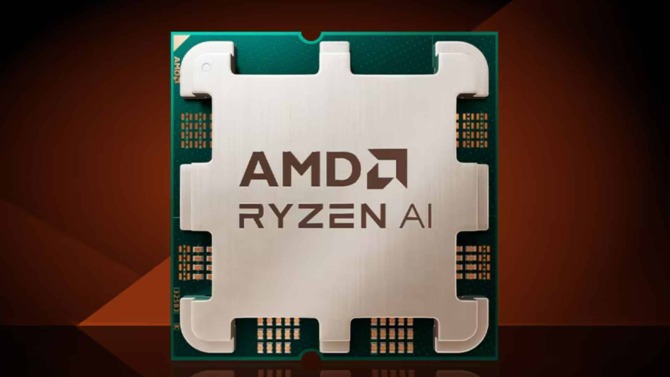

AMD Olympic Ridge — Новая информация об обновленном блоке CCD Zen 6, включая количество ядер и кэш-памяти

В этом году AMD представит первые серверные процессоры EPYC на базе микроархитектуры Zen 6 (серия EPYC Venice). Новые системы, как уже было подтверждено, будут производиться по 2-нм техпроцессу TSMC. В этом году компания также должна представить потребительские системы Ryzen из новой серии Olympic Ridge, также основанные на ядрах Zen 6. В Интернете появилась интересная информация о новом CCD-кластере, в котором будут размещены эти ядра.

По последней информации, блок CCD с ядрами Zen 6 должен иметь площадь 76 мм², что будет небольшим отличием от Zen 5 текущего поколения (около 71 мм²). Емкость кэша L3 также увеличится.

Тест процессора AMD Ryzen 7 9850X3D — новый король игровой производительности… Чуть более быстрый и гораздо более дорогой AMD Ryzen 7 9800X3D

По информации @HXL, CCD-блок в процессорах AMD на микроархитектуре Zen 6 будет иметь площадь примерно 76 мм². Для сравнения: нынешнее поколение ПЗС-матриц имеет размер примерно 71 мм². У Zen 4 это было ~72 мм², у Zen 3 — 83 мм², а у Zen 2 — 77 мм². Как видите, производитель сохраняет относительно схожие размеры последующих CCD-кластеров, а последний с ядрами Zen 6 будет всего примерно на 5% больше своего предшественника. Несмотря на относительно небольшое изменение размеров, сама структура претерпит изменения, которые понравятся пользователям.

Zen2 CCD: 2*4 ядра 2*16 МБ L3 TSMC N7 ~77 мм2

ПЗС-матрица Zen3: 8 ядер, 32 МБ L3 TSMC N7 ~ 83 мм2

ПЗС-матрица Zen4: 8 ядер, 32 МБ L3 TSMC N5 ~72 мм2

ПЗС-матрица Zen5: 8 ядер, 32 МБ L3 TSMC N4 ~71 мм2

ПЗС-матрица Zen6: 12 ядер, 48 МБ L3 TSMC N2 ~76 мм2

— HXL (@9550pro) 30 января 2026 г.

AMD подтверждает работу над микроархитектурой Zen 6 и Zen 7. Новое поколение карт Radeon будет ориентировано на трассировку лучей и искусственный интеллект.

Новый блок CCD теперь будет иметь 12 ядер Zen 6, благодаря чему топовые процессоры Olympic Ridge для потребительского рынка смогут предлагать 24-ядерную и 48-поточную конфигурацию. Кроме того, будет увеличен объем кэш-памяти L3 — вместо 32 МБ на одну CCD будет 48 МБ. В случае двух кластеров речь идет о 96 МБ вместо 64 МБ. Это должно привести к увеличению производительности в играх даже без использования 3D V-Cache. Блок CCD, также предназначенный для потребительского рынка, будет производиться по литографии TSMC 2 нм (говорят о варианте N2P), а блок ввода-вывода будет основан на техпроцессе TSMC N3P.

Источник: X @HXL, WCCFTech