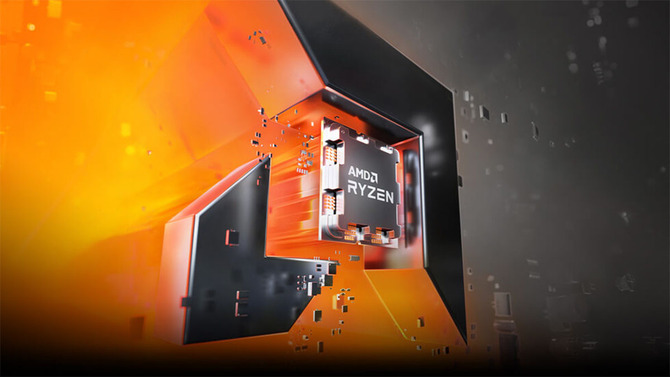

AMD ZEN 6 — Предстоящие процессоры Ryzen могут использовать новую технологию упаковки Info и TSMC -OS

AMD в Ryzen процессорах начали использовать технологию чипов с архитектурой Zen 2, когда впервые появилась внутренняя магистральная ткань Infinity. С тех пор строительство постоянно улучшалось — до последней архитектуры Ryzens 9000 и Zen 5 — но ее основная задача осталась неизменной. Теперь, однако, строительство этой автобуса может принципиально измениться, обеспечивая более низкое потребление энергии и более низкие задержки передачи данных.

Процессоры AMD Ryzen из семейства Олимпийских хребтов (ZEN 6) могут использовать новую технологию упаковки Info-OS TSMC и TSMC, известная из мобильной APU семейства Halo Strix, включая Ryzen AI Max+ Pro 395.

AMD Medusa Point и gator -диапазон с ядрами Zen 6 с премьерой в 2027 году. Озеро Intel Panther и озеро Wildcat в 2026 году

AMD в Ryzen процессорах от Zen 2 Architecture до Zen 5 использует автобус Infinity Fabric, основная задача которой — объединить вычислительные чипу с чип -пультом ввода -вывода. Это осуществляется фрагментом системы под названием GMI (Global Memory Interconnect). Соединение GMI может работать в двух режимах: GMI-Narrow или GMI-в последнем случае два GMI-Narrow работают вместе как одно, более широкое соединение. В потребительских процессорах чипа ввода/вывода оснащен двумя соединениями GMI-Narrow, каждый из которых поддерживает один из чипов расчета CCD, который на практике дает два независимых соединения. Однако в серверных единицах используется режим GMI, предлагающий гораздо более высокую емкость и лучшую эффективность связи.

AMD Olympic Ridge, Gator Drange и Medusa Point — процессоры Zen 6 в основном выиграют от литографии TSMC N2P

Почему это важно? Потому что отдельный GMI состоит из девяти блоков логики, которые касаются сериализации и дрессировки сигналов, то есть операций шнура. Это позволяет превращать параллельные сигналы (например, различные инструкции) в последовательные сигналы. Биты тщательно смешиваются с различными инструкциями и высвобождают их одной строкой, а затем извлекают и переворачивают их в правильный сигнал. Различие битов обусловлено специальными методами кодирования данных (например, 8b/10b, 64b/66b), которые гарантируют соответствующее количество переходов сигналов 0 — 1, благодаря которой приемник может восстановить часы из самого потока данных и знать, где каждый бит начинается и заканчивается. Кроме того, выравнивание и коррекция используются таким образом, чтобы сигнал на очень высоких частотах не смешивается в шум. Благодаря этому можно отправить большое количество данных с меньшим количеством физических линий, но за счет дополнительных задержек и увеличения потребления энергии для операций шнура и высокой тактовой скорости тканевой шины Infinity.

AMD EPYC VENICE — Новая информация о спецификациях и энергопотреблении процессоров сервера Zen 6 и Zen 6C

Конечно, можно решить эту проблему, не используя весь механизм шнура, напрямую подключив выходы ввода/вывода с помощью вычислительной чипу CCD. Тем не менее, это требует использования очень плотной сетки подключения, называемой AMD как «море проводов». Такая бесконечная тканевая шина в топологии вентилятора требует чрезвычайно точного процесса упаковки и высококачественных органических интерфейсов — пластиковые ламинаты с медными путями микроскопических размеров. Дополнительным условием является прямое окрестности ПЗС и чип -палаты ввода -вывода. Взаимосвязь, построенная таким образом, позволяет устранить задержки, возникающие в результате операции, и значительно снижает потребление энергии (предполагаемое снижение до 0,2 PJ/бит от 2 PJ/BIT) и высвобождает ценное место для других элементов CPU.

Первые инженерные образцы нового поколения процессоров AMD Ryzen, основанные на ядрах Zen 6, отправились в партнеры компании.

Стоит добавить, что это решение больше не является только концепцией, которая существует в готовых продуктах, потому что TSMC Info-OS-технология, которая используется мобильной APU из семейства Halo Strix, используется для таких упаковочных чипов, включая Ryzen AI Max+ Pro 395. Это предлагает высокую вероятность использования этого типа и изменений в Interconnect также в будущем Ryzen-процессе. Тем не менее, реализация 3D V -CERA остается открытой проблемой, потому что подключение ее с плотной сеткой кабелей под системой может быть очень технологически сложным, поэтому существует вероятность того, что кэш снова перейдет на вершину ПЗС. В этом контексте высокая доходность YouTuber указывает на то, что системы APU Strix Halo фактически предлагают заметно более высокую емкость данных и более низкие задержки благодаря новому подходу к взаимосвязи. Сравнение, однако, не является идеальным, потому что оно объединяет APU с процессором и, следовательно, различные классы систем. Несмотря на это, это можно увидеть в большом потенциале, если AMD решит аналогичное решение в Zen 6, и это может принести реальные преимущества, хотя сейчас это только косвенные доказательства.

https://www.youtube.com/watch?v=mah6kz0ykxu

Источник: TechPowerup, yt (@High Liking)