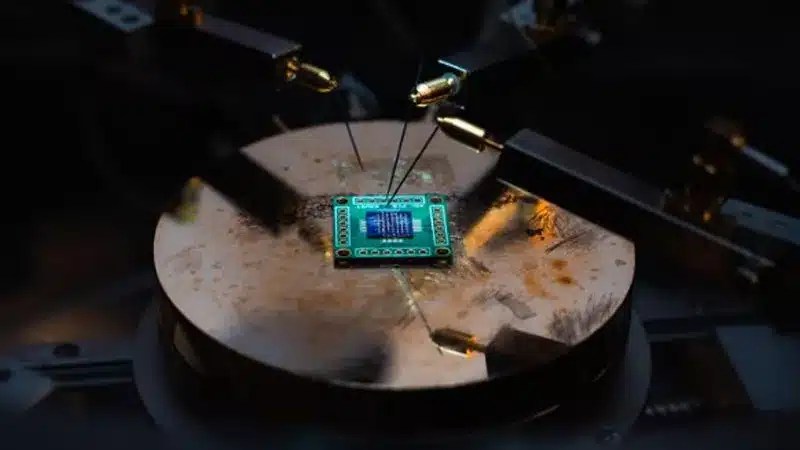

Электроника достигла новых высот: ученые впервые разместили 6 КМОП-транзисторов друг на друге

Группа ученых из Университета науки и технологий имени короля Абдаллы в Саудовская Аравия (КАУСТ) установил рекорд производства микросхем, создав первую в мире шестиуровневую гибридную схему КМОП (дополнительная структура). Рекорд ранее принадлежал бельгийской компании Imec, разработавшей двухкаскадную структуру CFET. Разработчики микросхем ограничены площадью кристалла, и расположение транзисторов друг над другом — это один из способов пойти еще дальше.

Разработка описана в статье в журнале Nature Electronics. В схеме объединены оксидные тонкопленочные транзисторы n-типа (ОхТс) и органические тонкопленочные транзисторы p-типа (ОрЦ), предназначенный для массового производства электроники, включая гибкие дисплеи, носимые датчики и устройства IoT.

Авторы подчеркивают растущий спрос на интегральные схемы с низким энергопотреблением, механической гибкостью и возможностью крупносерийного производства, где традиционное горизонтальное расположение схем и элементов сталкивается с ограничениями с точки зрения разрешения и стоимости. Вертикальная интеграция обеспечивает более высокую плотность транзисторов, меньшую длину межсоединений и минимизацию паразитных задержек при адаптации к низкотемпературным производственным процессам, что имеет решающее значение для ряда материалов, а также для многослойных чипов, склонных к перегреву из-за высокой плотности мощности.

Предыдущие разработки ограничивались двумя слоями из-за проблем с выравниванием склеиваемых поверхностей и перегрева многослойных растворов. Однако предлагаемая платформа преодолевает эти препятствия, демонстрируя рекордные 6 транзисторных стеков с 41 технологическим слоем.

Шестислойная структура изготавливается посредством 40-этапного процесса литографии на кремниевых подложках, начиная с буферного изолирующего слоя толщиной 2 мкм (микрометра).

Электроды (Al для OxT и Ti/Au для OrT) осаждаются путем физического осаждения пара (ПВД) на малой мощности для минимизации шероховатостей (<1 нм). Весь процесс проводили при комнатной температуре или нагреве не выше 100°С во избежание термического повреждения нижележащих слоев. Размеры транзисторов были разными: длина затвора 10 мкм для n-типа и 3 мкм для p-типа, с чередованием типов для балансировки токов.

Производительность транзистора была оценена на 600 устройствах, и на нижних уровнях были показаны лучшие результаты. Гибридные инверторы (300 устройств), построенные из пилотных матриц, достигли максимального усиления 94,84 В/В, напряжения переключения 0,93–2,61 В и потребляемой мощности 0,47 мкВт. Также были протестированы логические элементы на основе 6-уровневых транзисторов – в частности, элементы ИЛИ и другие.

Предлагаемая платформа открывает путь к созданию высокоплотных и энергоэффективных схем для крупногабаритной электроники, превосходящих предыдущие двухслойные аналоги по плотности и производительности. Улучшенное качество соединений между слоями и использование низкотемпературных процессов обеспечивают совместимость с гибкими подложками, снижая паразитные эффекты и увеличивая производительность. Авторы подчеркивают потенциал своих разработок для производства логики, памяти и датчиков, что может привести к революции в области энергоэффективных решений. Дальнейшие исследования будут сосредоточены на оптимизации верхнего слоя и его интеграции с большими подложками, что необходимо для приготовления коммерческих продуктов.