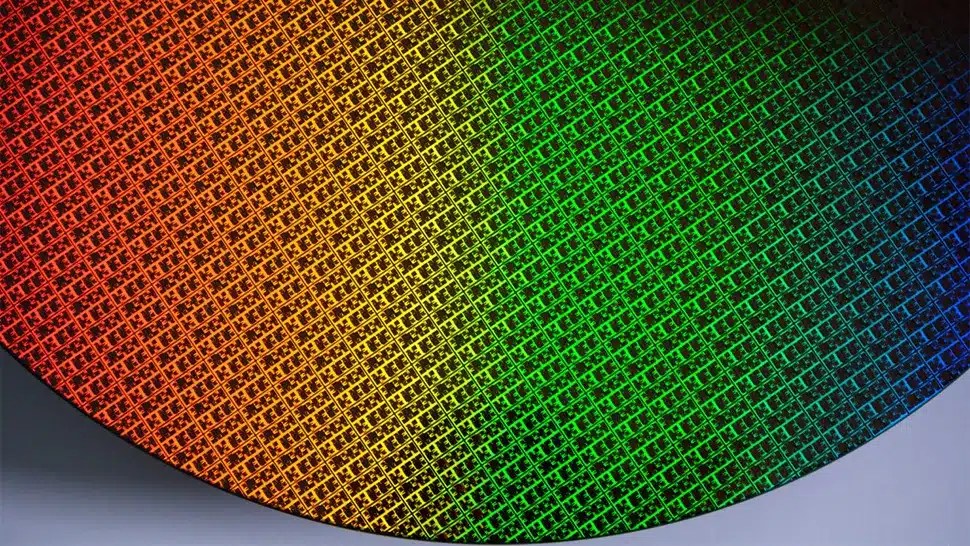

IMEC представили транзисторы следующего поколения — они быстрые, эффективные и доступные для производства

Около 6 лет назад бельгийский центр IMEC представил совершенно новую транзисторную архитектуру — CFET (Дополнительные полеты) Он должен был помочь производить транзисторы со скоростью ниже 2 нм. Архитектура характеризуется отдельными постепенными каналами власти (Викшет) Тем не менее, технология оказалась трудной для производства, поэтому IMEC создал модифицированную промежуточную версию будущей архитектуры, которая была представлена несколько дней назад.

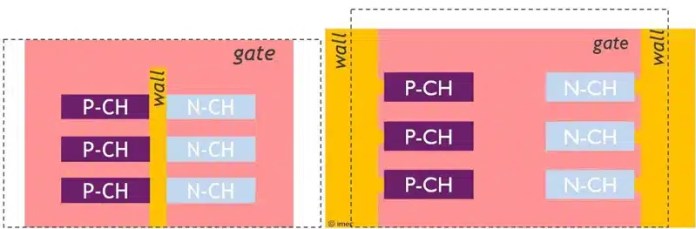

Суть архитектуры виклана заключается в разделении транзисторов GAA от N- и P-типа на диэлектрический барьер.

Барьер или стена предназначены для минимизации влияния соседних транзисторов друг на друга. В этом случае пара транзисторов с различной проводимостью может быть сделана на меньшей площади чипа, что приводит к значительному снижению площади чипа до 20 %. Кроме того, IMEC предлагает поместить транзисторы друг на друга, чтобы реализовать архитектуру CFET, которая еще больше уменьшит площадь чипа. Тем не менее, последующая работа по транзисторам с разделенными страницами показала, что идея диэлектрического барьера была чрезвычайно трудно реализовать при производстве.

Самый тонкий диэлектрический барьер с толщиной от 8 до 10 нм должен был быть произведен в первую очередь, даже перед всеми манипуляциями с кристаллами и травлением транзисторов. Не каждый материал может противостоять такому «злоупотреблению», которое приведет к высоким уровням дефектов. Затем ИМЕК предложил блестящее решение — барьеры должны быть внешними. Они больше не дистанцируются многополярные транзисторы друг от друга, но изолируют пары транзисторов от соседних пар. На самом деле, это изоляция транзисторов той же проводимости.

С этим процессом барьеры стали одним из последних из кристалла. Это решение позволяет использовать знакомые материалы. Из -за более толстых стен площадь паров транзисторов может быть немного затронута, но все другие преимущества в виде высокой скорости (течения) и уменьшенная утечка осталась. Более тонкий переход между носовой и внешней стенкой позволил воротам покрывать увеличенную площадь на краю каждого нано, что значительно улучшило контроль токов транзисторных каналов.

Наконец, окончательное производство внешних стен вокруг транзисторных каналов увеличивало механическое напряжение в Nappic (в транзисторных каналах). Термин «напряженный кремний» известен всем, кто участвовал в производстве чипов в течение как минимум четверти века. В таких условиях проводимость увеличивается.

Разработчики признают, что с увеличением толщины внешних изоляционных барьеров между транзисторами до 15 нм общая площадь чипа может быть немного больше, чем в случае использования внутренних разделов, но это небольшая и необходимая жертва. Моделирование CAD клеток SRAM и генераторов с использованием транзисторов с нанолистами с внешними барьерами показало, что в статических ячеек памяти новый технологический процесс технологического процесса A10 (10 Angstrom) Уменьшает площадь на 22% по сравнению с нанолистом A14 без изоляции, что связано с более плотной упаковкой устройств того же типа и стадией уменьшенного затвора.

Для полных схем осцилляторов новая схема соответствует или превышает производительность осцилляторов для технологических процессов A14 и 2 нм. При пустой нагрузке источник питания уменьшается примерно на 33% (снижение)

Опыт производства разделенных завышенных транзисторов будет важен для разработки CFET, так как многие технологические шаги, материалы и концепции для дизайна будут перекрываться. В транзисторах для вилокна, устройства P-типа и N-типа расположены рядом. Напротив, в следующем поколении CFET два различных типа транзисторов будут расположены вертикально, хотя основная технология останется прежней, но это история с середины 1930-х годов, на которую мы вернемся много раз в будущем.