Intel инвестирует в EUV с высоким содержанием и развивает транзисторы CFET. Новая стратегия борьбы за преимущество в продвинутом производстве чипов

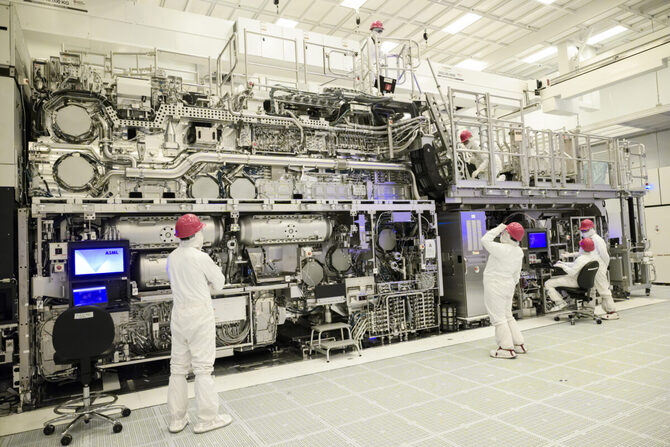

Технология производства чипов является наиболее важным элементом современной электроники, стимулируя разработку процессоров, видеокарт и других компонентов. Такие компании, как ASML, Intel или LAM Research, работают над все более продвинутыми методами, которые позволяют вам создавать гораздо меньшие и более эффективные системы в течение многих лет. Наряду с эволюцией производственных процессов появляются новые подходы, которые могут изменить будущее отрасли.

CFET позволяют вам почти удвоить плотность транзисторов, благодаря вертикальному укладке N-IP-FET над собой.

Google и TSMC ведет переговоры о контракте на Tensor G5 Systems, произведенные в процессе 3 нм для пиксельных смартфонов с 2025

Intel объявила, что в суде 14А он достигнет литографии высокого euv. Это шаг, который должен укрепить свои позиции в конкуренции с TSMC на рынке добычи контракта. Машины ASML нового поколения предлагают более высокое разрешение, но каждый из них стоит до 370 миллионов долларов. TSMC подходит к теме более тщательно. До 1,4 нм намеревается использовать текущие решения с низким уровнем -На, чтобы избежать резкого увеличения затрат. В контексте подготовки к реализации High -NA EUV Intel также сотрудничает с LAM Research, которое предоставляет решения, поддерживающие новые литографические процессы. Это даже усовершенствованные системы осаждения, а также пищеварение полупроводниковых слоев.

TSMC объявляет SOW-X, новую эру упаковочных чипов для AI и HPC. Массовое производство начнется в 2027 году

Параллельно развивается технология CFET, то есть три -мерные транзисторы, в которых элементы NFET и PFET изложены один над другим. Intel, Samsung и TSMC работают над своей реализацией, планированием использования на 2,5 нм и меньших процессах, и в конечном итоге даже около 1 нм. Эта конструкция позволяет значительно увеличить плотность упаковки транзисторов и улучшить электростатический контроль, одновременно уменьшая поверхность всей системы. На практике это означает, что отрасль развивается в двух направлениях одновременно, то есть все более и более точной литографии и новой транзисторной архитектуры. Вполне возможно, что последующие поколения интегрированных процессоров и систем будут отличаться не столько технологическим процессом, сколько самого технологического процесса, а плотность и эффективность.

Источник: Reuters/CA Finance, Wccftech, Semiviki, TSMC