Intel показала образец огромного ИИ-чипа с четырьмя логическими блоками и 12 стеками HBM4

Intel Foundry опубликовала официальный документ с подробным описанием передовых решений компании для разработки и внедрения аппаратного обеспечения для приложений искусственного интеллекта и высокопроизводительных вычислений.

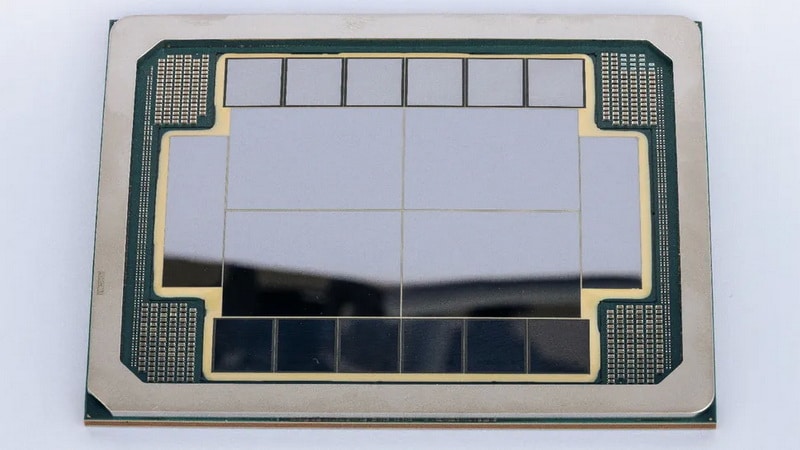

Intel также продемонстрировала «модель для тестирования чипов искусственного интеллекта», демонстрирующую текущие возможности компании в области упаковки.

Intel продемонстрировала систему в упаковке (Система в упаковке, SiP) размером с восемь стандартных фотомасок микросхем, включающих четыре логических блока, 12 стеков класса HBM4 и два блока ввода-вывода. В отличие от крупномасштабной концепции HBM5 с 16 логическими блоками и 24 стеками, которую компания представила в прошлом месяце, эта система фактически готова к производству уже сегодня.

Важно отметить, что Intel Foundry показала не работающий ИИ-ускоритель, а скорее «тестовые модели ИИ-чипа» (как уже упоминалось), который демонстрирует, как можно физически создавать будущие процессоры и высокопроизводительные вычисления (точнее в сборе). Intel демонстрирует целый метод проектирования, который сочетает в себе большие вычислительные блоки, высокоскоростные стеки памяти, сверхбыстрые межкристальные соединения и новые технологии электропитания в одном процессорном корпусе. Этот пакет сильно отличается от того, что предлагают сегодня такие компании, как TSMC. Intel хочет показать, что процессоры следующего поколения для высокопроизводительного искусственного интеллекта могут иметь многочиповую конструкцию и что компания уже способна их производить.

Демонстрируемая платформа основана на четырех больших логических блоках, вероятно, построенных по техпроцессу Intel 18A (следовательно, с транзисторами RibbonFET с круглым затвором и системой питания PowerVia сзади), которые окружены стеками памяти класса HBM4 и блоками ввода-вывода.

Все ключевые элементы предполагается подключать через мосты ЭМИБ-Т 2.5D, встроенные непосредственно в площадку шасси. Intel использует технологию межчипового интерфейса EMIB-T, которая добавляет кремний через отверстия внутри мостов, чтобы мощность и сигналы могли проходить как вертикально, так и горизонтально, чтобы максимизировать плотность межсоединений и подачу мощности. Платформа предназначена для межчиповых интерфейсов UCIe, работающих со скоростью 32 ГТ/с и выше, которые, судя по всему, также используются для соединения стеков C-HBM4E.

Тестовый образец также демонстрирует переход Intel к вертикальной сборке. Дорожная карта компании включает технологию Intel 18A-PT, разработанную специально для чипов, которые предусматривают размещение других логических микросхем или памяти поверх них. Следовательно, чиплеты должны иметь питание на задней стороне и использовать гибридные соединения. В случае «тестовой модели» базовые кристаллы 18A-PT расположены под вычислительными кристаллами 18A/18A-P и действуют как большие микросхемы кэша или выполняют какую-либо другую вспомогательную функцию. Intel использует семейство технологий упаковки Foveros — Foveros 2.5D, Foveros-R и Foveros Direct 3D — для вертикального соединения чипсетов. Они обеспечивают точное медное соединение между активными кристаллами, чтобы максимизировать пропускную способность и энергоэффективность вышеупомянутых кристаллов. Вместе с мостами EMIB эти технологии позволяют Intel создать гибридное горизонтально-вертикальное крепление, которое компания позиционирует как альтернативу большим кремниевым переходникам с более высоким коэффициентом использования пластин и более высокой производительностью.

В многочиповых ускорителях искусственного интеллекта и высокопроизводительных вычислениях основным ограничением при проектировании является мощность.

С этой целью платформа Intel должна интегрировать все последние инновации Intel в области энергосбережения, включая PowerVia, встроенные конденсаторы Omni MIM, развязку на уровне моста в конденсаторах EMIB-T, eDTC и eMIM-T на базовом чипе, а также встроенные катушки индуктивности CoaxMIL для поддержки полуинтегрированных регуляторов напряжения (IVR), расположенных под каждым стеком и под самим корпусом (в отличие от IVR в случае с TSMC). CoWoS-L, входящие в состав интерпозера). Эта многоуровневая сеть предназначена для поддержания стабильного тока при генеративных нагрузках AI без снижения уровня напряжения.

Своей демо-версией Intel явно пытается привлечь клиентов. Пока неизвестно, будет ли ускоритель искусственного интеллекта следующего поколения под кодовым названием Jaguar Shores, выпуск которого запланирован на 2027 год, использовать архитектуру, продемонстрированную сегодня Intel.