TSMC будет производить гигантские чипсы, в 40 раз быстрее, чем сегодня

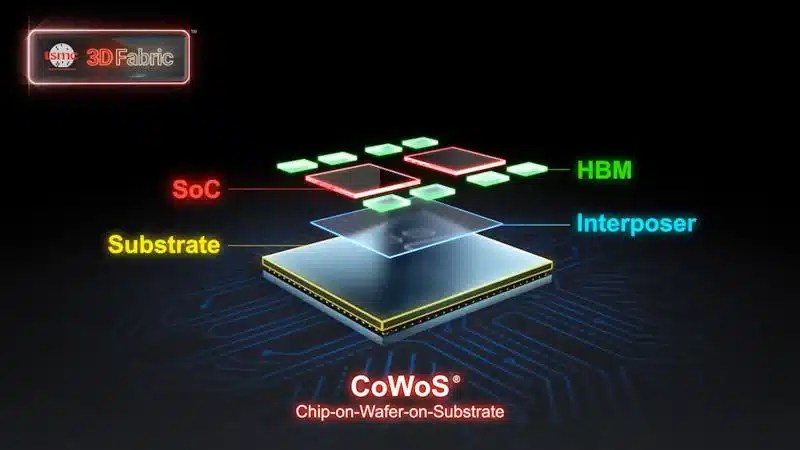

Размеры современных процессоров, как правило, небольшие, но крупнейший производитель полупроводников в мире TSMC разрабатывает новую версию своей технологии Cowos Chip, которые можно использовать для создания структур до 9,5 фото маски (7885 мм²) на пластинах размером 120 × 150 мм (18 000 мм²)

Продуктивность таких гигантских чипов будет в 40 раз выше, чем у современных процессоров, но это не ограничение.

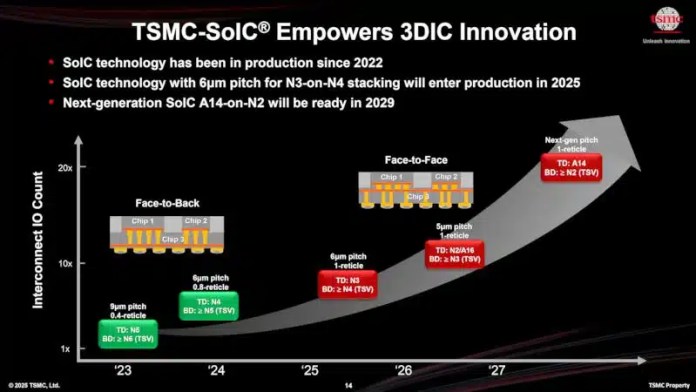

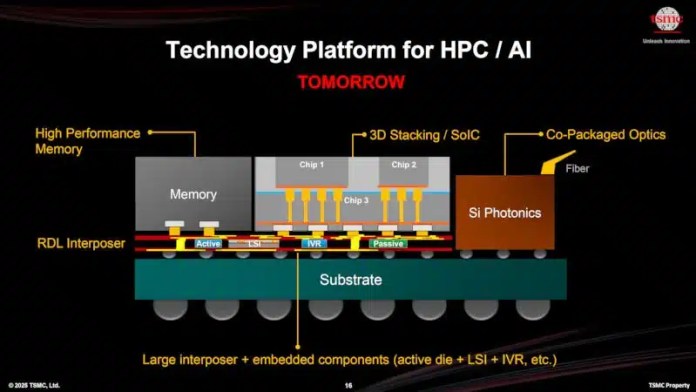

Почти все современные процессоры с высокой производительности, предназначенные для центров обработки данных, уже многочисленны. Поскольку спрос на более быстрые решения растет, разработчики стремятся интегрировать еще больше кремния в свои системы. Стремясь реагировать на этот поиск, TSMC расширяет свои варианты обертывания чипов и делает их еще больше. На своем мероприятии, североамериканском технологическом симпозиуме, компания показала свою дорожную карту 3DFABRIC: промежуточные слои будут расти далеко за пределами возможностей этой технологии.

Текущая версия технологии упаковки Cowos TSMC позволяет использовать промежуточные слои до 2831 мм²-в три раза больше размера фото маски: стандарт для экстремальной ультрафиолетовой литографии (Эв) составляет 858 мм², а TSMC использует 830 мм². AMD Instinct MI300X и NVIDIA B200 с двумя большими логическими чипами и восемью стеками памяти HBM3 или HBM3E уже достигли этой границы.

Тем не менее, этого уже недостаточно для будущих процессоров. В следующем году или чуть позже TSMC представит новую технологию упаковки Cowos-L, которая поддерживает промежуточные слои до 4719 мм²-это примерно в 5,5 раза больше, чем область стандартной фотомаски. Такие пакеты будут включать до 12 стеков памяти и потребуется большая пластина 100 × 100 мм (10000 мм²) Решения, основанные на такой архитектуре, позволят в три раза более высокую вычислительную производительность, чем текущие проекты. Этого будет достаточно для акселераторов Nvidia Rubin, например, с 12 стеками HBM4, но в будущем это потребует больше мощности.

В будущем TSMC намерен предложить своим клиентам промежуточные слои до 7885 мм² — 9,5 раза больше, чем максимально возможная фотомаска, расположенная на пластине 120 × 150 мм.

Для сравнения, стандартный размер коробки CD составляет приблизительно 125 × 142 мм. В прошлом году компания рассказала о нескольких структурах, размеющих 120 × 120 мм (Примерно в восемь раз больше фотомаммы) И кажется, что рост этого показателя отражает спрос клиентов. Такой дизайн будет включать в себя четыре компонента с вертикальным расположением кристаллов SOIC (например, кристалл N2 или A16 на логике n3), 12 стеков HBM4 и дополнительные кристаллы ввода/вывода.

У TSMC есть клиенты, которые хотят максимально возможной производительности и готовы заплатить за это. Для них компания предлагает технологию System-On-Wafer (SOW)-производство чипов с размером кремниевой пластины.

До сих пор только церебра и Тесла выиграли от этой возможности, но TSMC уверен, что другие клиенты присоединятся к ним. Обновленная технология SOW-X, основанная на копо, позволит создать многоточечный и кремний размер, на котором могут быть установлены память HBM и оптические соединения. Предполагается, что SOW-X будет представлен в 2027 году.

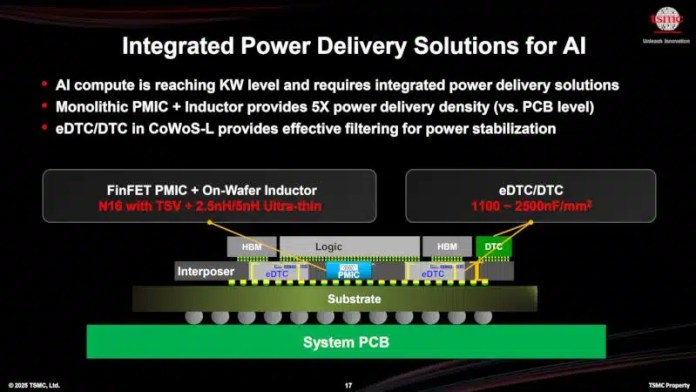

Процессоры размером с маски в 9,5 раза больше, чем максимально возможная фотомаска или даже размер пластины, требуют значительных усилий по производству и сборке. Одной из основных проблем является источник питания: такие чипы требуют мощности киловатта и высокого тока. Для производителей серверов становится все труднее решать эту проблему самостоятельно, поэтому она должна быть решена на систематическом уровне. TSMC предлагает интегрировать монолитные интегрированные схемы управления питанием (PMIC) с вертикальTSV) Сделано с помощью технологии и индукторов N16 Finfet, установленных на пакете Cowos-L с RDL (Перераспределение уровня) Интерпозеры. Это позволит направить мощность через пластину, уменьшая расстояние между источниками питания и активными кристаллами, что, в свою очередь, снизит паразитное сопротивление и улучшит целостность питания.

TSMC сказал, что технология PMIC N16 обеспечивает более точный контроль над энергоснабжением для переработчиков. Это особенно важно для многократных проектов и многочисленных проектов, где рабочие нагрузки могут быстро измениться, но необходимо поддерживать стабильную производительность системы. Схема обеспечивает точную настройку с динамическим масштабированием натяжения (DVS) при заданном количестве электричества. По сравнению с традиционными подходами плотность власти увеличивается пять раз.

Подход TSMC отражает изменение системной оптимизации: энергоснабжение уже рассматривается как неотъемлемая часть кремния, упаковки и общей конструкции, а не как отдельная функция каждого компонента.

Увеличение размера промежуточного модуля окажет влияние на проектирование системы, особенно в отношении форм-фактора пакета. PAD 100 × 100 мм почти на форме OAM 2.0 (102 × 165 мм) Будущая площадка 120 × 150 мм уже превышает, и, вероятно, необходимо будет ввести новые стандарты для модулей и плат. Кроме того, аналогичные системы «системы в пакете» (Глоток) генерировать огромное количество тепла. Чтобы решить эту проблему, производители уже изучают новые методы охлаждения, включая прямое жидкое охлаждение, которое NVIDIA использует в своем GB200/GB300 NVL72, а также технологии погружения, чтобы помочь справиться с теплом, генерируемым мультицинеле, и это задача, которую TSMC не может.