TSMC объявляет о Copos и PLP. Значительная эволюция, которая позволит вам получить больше места для чипсов

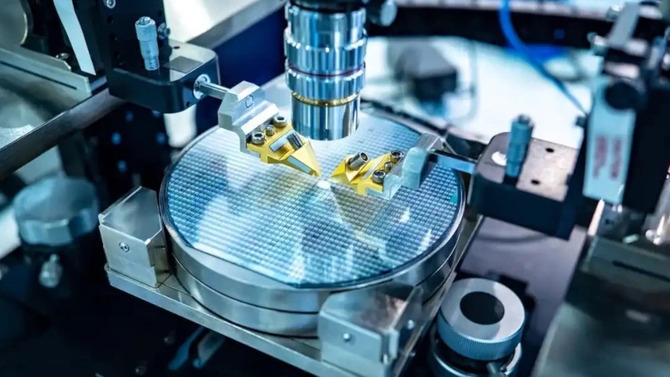

TSMC, тайваньский гигант и мировой лидер полупроводниковой промышленности, разрабатывает передовые технологии, используемые в течение многих лет, в том числе через Nvidia, AMD, Intel, Apple и другие крупнейшие технологические компании. Новая информация о планах компании появилась в сети, в следующем году TSMC намерен запустить пилотную производственную линию для современных методов упаковки капо и чипа PLP. Цель состоит в том, чтобы разработать технологии и ее реализацию в производстве.

TSMC объявляет о запуске пилотной производственной линии для современных методов упаковки капо и чипа PLP, которые будут использовать квадратные субстраты. Цель состоит в том, чтобы разработать технологии и ее реализацию в производстве в ближайшие годы.

TSMC объявляет SOW-X, новую эру упаковочных чипов для AI и HPC. Массовое производство начнется в 2027 году

TSMC, как и вся полупроводниковая индустрия, является постоянной проблемой: как поместить все больше и больше транзисторов в интегрированных цепях. Поскольку скорость миниатюризации явно замедляется, а спрос на вычислительную власть, особенно в связи с развитием искусственного интеллекта, растет в головокружительных темпах, чипы становятся все больше и больше. Это, в свою очередь, приводит к более высоким производственным затратам и трудностям при получении. Одним из решений является сочетание множества интегрированных цепей на одном субстрате, но здесь тоже начинается пространство. В ответ на эти ограничения TSMC разрабатывает новые технологии, которые должны значительно увеличить поверхность, доступную для упаковки чипов. Так был создан проект Copos — преемник технологии Cowos. В то время как текущее поколение (Cowos) позволяет создавать пакеты с размерами максимум 120 × 150 мм, новый метод Copos должен позволить этому пространству увеличиться до 310 × 310 мм. Согласно доступной информации, NVIDIA будет первым клиентом, который использует Copos.

Отчет TrendForce: Samsung падает на 11,3%, SMIC растет — расстояние сокращается, а TSMC остается лидером

Упаковка Copos использует квадратные субстраты, что облегчает как планирование, так и установку чипов, что позволяет одновременно размещать их больше. Технология PLP (упаковка на уровне панели), используемая как часть Copos, заключается в том, чтобы использовать гораздо большие панели в будущем, даже с размерами 600 × 600 мм, что также открывает путь к использованию будущих стеклянных подложков. Согласно сообщениям, TSMC планирует запустить пилотную производственную линию для Copos в следующем году. Он должен служить дальнейшей исследованиях и разработках по практической реализации новых технологий. Цель компании — разработать полное решение к концу 2027 года, которое в 2028 году будет одобрена партнерами. Тем не менее, первые реальные продукты, использующие Copos, появятся в конце 2028 года или в начале 2029 года.

Источник: ComputerBase