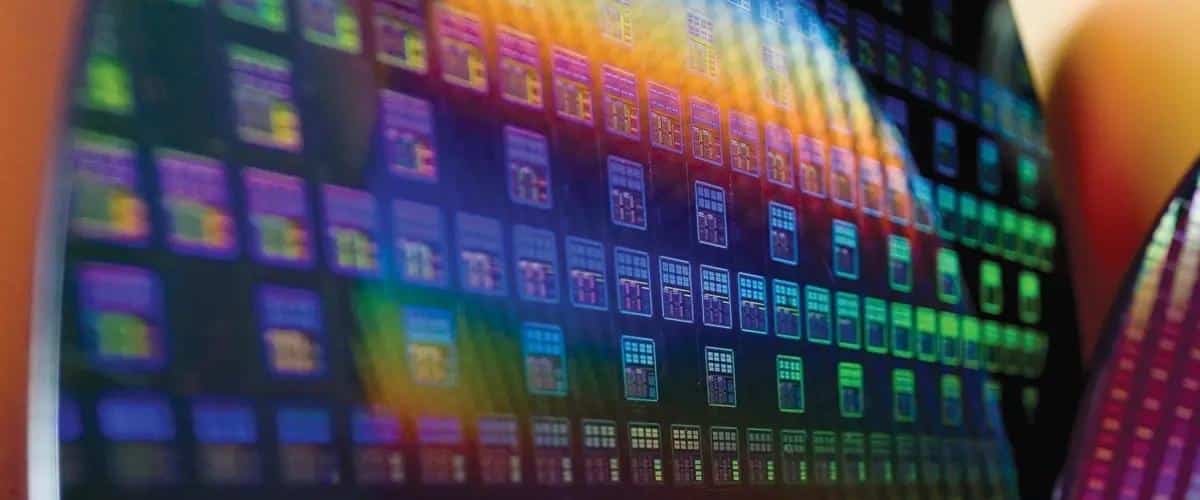

К 2029 году TSMC начнет производить чипы по 1,2-нм и 1,3-нм процессам на современном оборудовании.

Тайваньский гигант TSMC представил обновленную дорожную карту развития полупроводниковых технологий до 2029 года на Североамериканском технологическом симпозиуме. Акцент был сделан на новых технологиях 1,2-нм и 1,3-нм классов – А12 и А13, а также на 2-нм решениях. Запуск A16, заказчиком которого должна была стать Nvidia, был перенесен на 2027 год. Кроме того, TSMC сознательно отказалась от использования сверхдорогих литографов High-NA EUV на ближайшие несколько лет, предпочитая увеличивать масштаб текущих решений.

Одним из главных анонсов стал процесс A13, который станет развитием A14 и будет запущен в 2029 году. Как и в случае с более ранним 2-нм техпроцессом, A13 сохранит транзисторы типа GAA — компания делает ставку на постепенное масштабирование без резких технологических скачков, что снижает риски с точки зрения сроков и выхода хороших кристаллов. Новый процесс обеспечит увеличение плотности транзисторов на 6% за счет оптического уменьшения размеров, сохраняя при этом совместимость с существующими стандартами проектирования и электрическими параметрами. Это позволит клиентам воспользоваться преимуществами более высокой плотности транзисторов с минимальным изменением конструкции.

Параллельно компания расширяет линейку 2-нм решений новым узлом. Н2У. Это будет третье поколение платформы N2, которое обеспечит прирост производительности на 3–4% или снижение энергопотребления на 8–10% без перехода на совершенно новую архитектуру. Это особенно важно для производителей бытовой электроники, где ключевую роль играют стоимость и возможность повторного использования IP-блоков.

TSMC также переходит к раздельной стратегии развития технологических процессов. Теперь компания будет ежегодно выпускать новые узлы для потребительских устройств, таких как смартфоны, и каждые два года для требовательных приложений, включая искусственный интеллект и высокопроизводительные вычисления. Такой подход отражает меняющийся рынок: если раньше мобильные устройства были основным источником дохода, то теперь драйверами роста являются искусственный интеллект и центры обработки данных.

Для этих приложений TSMC разрабатывает отдельную линейку технологий, включая A16 и будущую A12. Они ориентированы на максимальную производительность и используют архитектуру с задним приводом (Суперсиловая железная дорога) для повышения эффективности и плотности транзисторов. Массовое производство A16 ожидается в 2027 году, а A12 станет следующим шагом в 2029 году.

TSMC также разрабатывает упаковочные решения. Технология CoWoS (чип на пластине на подложке) позволит к 2028 году объединить в одном чипе до 10 вычислительных кристаллов и до 20 стеков памяти HBM. Для 3D-интеграции компания готовит обновленную версию SoIC (System on Integrated Chips): к 2029 году плотность межсоединений увеличится примерно в 1,8 раза, что обеспечит более плотное соединение кристаллов и более быстрый обмен данными. Новый продукт будет совместим с технологическими процессами уровня А14.

Интересно, что в технологиях A13 и A12 не планируется использовать EUV-литографию High-NA как минимум до 2029 года. Цена одного такого сканера от ASML может достигать 350-380 миллионов долларов. В отличие от Intel, которая опирается на эту технологию, TSMC предпочитает максимально использовать текущие решения EUV, избегая высоких затрат на новое оборудование. В компании подчеркивают, что эта стратегия уже приносит свои плоды: инженеры продолжают искать способы увеличения масштабов без перехода на более дорогие технологии.

Все важное из мира технологий прямо на ваш почтовый ящик.

Все важное из мира технологий прямо на ваш почтовый ящик.

Подписываясь, вы принимаете наши Условия и Политику конфиденциальности. Вы можете отказаться от подписки одним щелчком мыши в любое время.