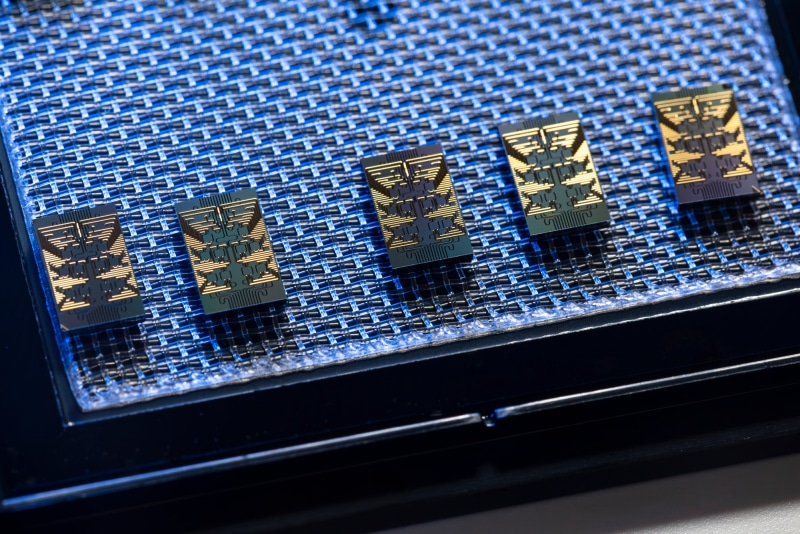

TSMC представляет последний план выпуска своей литографии, включая процессы N2U, A14, A13 и A12.

TSMC на данный момент остается лидером среди компаний, внедряющих технологические процессы последнего поколения. Именно TSMC производит большинство современных интегральных схем, включая процессоры и графические блоки. В последние годы TSMC практически доминировала на этом рынке, что, очевидно, привело к значительному росту цен на кремниевые пластины для клиентов компании. В свою очередь, внедрение последующей, все более совершенной литографии, прошло относительно гладко. Какие планы у компании на ближайшие годы?

Во время Североамериканского технологического симпозиума компания TSMC представила свой последний план по внедрению дальнейших технологических процессов. В него входят такие литографии, как N2U, A14, A13 и A12.

Samsung Foundry борется за 2 нм, но TSMC уходит. Более низкий выход SF2 усложняет планы Qualcomm

Новые технологические процессы от TSMC, которые будут реализованы до конца этого десятилетия, разрабатываются для таких улучшений, как уменьшение площади поверхности чипа и использование новых технологий для снижения энергопотребления, при этом не обязательно с учетом использования новейших станков ASML High-NA EUV. В этом году планируется реализовать улучшенную литографию N2P и N3A, основанную на ранее разработанном узле N2 и нацеленную на еще более высокую производительность (N2P) или более высокую энергоэффективность (N3A). В то время как N2P и N3A нацелены на продукты «High-end», одновременно должна быть реализована линейка N3C, то есть более дешевый узел для продуктов «Mid-to-Low-End».

TSMC расширяет возможности упаковки. Ожидается, что CoWoS, CoPoS и SoIC откроют рынок чипов искусственного интеллекта.

Одной из производных технологического процесса TSMC N2 станет N2U. Ожидается, что по сравнению с базовой 2-нм версией вариант N2U будет иметь производительность на 2–4% выше или снижение требований к энергопотреблению в диапазоне от 8 до 10%, сохраняя при этом тот же уровень производительности, что и базовый N2. N2U также будет поддерживать плотность на 2–3% выше, чем N2P. Производство литографии N2U начнется в 2027 году для сегмента Mainstream и в 2028 году для продуктов High-End, ориентированных в основном на расчеты AI и HPC.

Intel Foundry расширяет инфраструктуру упаковки микросхем в Малайзии. Инвестиции в размере 7,1 млрд долларов США против монополии CoWoS TSMC

О литографии TSMC A14 (класс 1,4 нм) мы уже знали, но в ходе Симпозиума были раскрыты первые подробности о двух следующих технологических процессорах: A13 (класс 1,3 нм) и A12 (класс 1,2 нм). Первый является естественным развитием базового A14, предлагая уменьшение площади на 6%. TSMC A13 должен стать золотой серединой для подготовки небольших систем при сохранении высокой производительности. Несмотря на сокращение занимаемой площади, ожидается, что A13 останется полностью обратно совместимым с процессом A14, что упростит его внедрение на производственных линиях. TSMC A13 поступит в производство в 2029 году. Второй разработкой A14 станет A12. Это будет первая литография, в которой будет использоваться технология заднего привода под названием Super Power Rail, конкурентное решение Intel PowerVia, представленное в своей первой версии с процессом Intel 18A. Узел 12А будет запущен одновременно с А13, то есть в 2029 году, через год после дебюта А14. Параллельно TSMC разрабатывает технологию упаковки CoWoS (Chip-on-Wafer-on-Silicon). В настоящее время реализуется версия с размером сетки 5,5, а к 2028 году планируется представить гораздо более обширную версию с размером сетки 14. Это означает интеграцию до 10 вычислительных систем и 20 стеков памяти HBM в рамках одной большой системы. Это только план на 2028 год, потому что в 2029 году ожидается появление еще более продвинутой версии CoWoS (так называемого SoW-X) с размером ячейки 40.

Источник: WCCFTech